US 20160171927A1

(19) United States

(12) Patent Application Publication

KANG

(10) Pub. No.: US 2016/0171927 A1

(43) Pub. Date: Jun. 16, 2016

(54) PIXEL AND ORGANIC LIGHT EMITTING

DISPLAY USING THE SAME(71) Applicant: SAMSUNG DISPLAY CO., LTD.,

Yongin-si (KR)

(72) Inventor: Chul-Kyu KANG, Yongin-si (KR)

(21) Appl. No.: 15/051,715

(22) Filed: Feb. 24, 2016

(52) U.S. Cl.

CPC ..... G09G 3/325 (2013.01); G09G 3/3266

(2013.01); G09G 3/003 (2013.01); G09G

2300/0426 (2013.01); G09G 2300/0439

(2013.01); G09G 2300/0809 (2013.01); G09G

2310/08 (2013.01); G09G 2330/00 (2013.01)

(57)

## ABSTRACT

## Related U.S. Application Data

(63) Continuation of application No. 13/137,899, filed on

Sep. 21, 2011, now Pat. No. 9,275,567.

## (30) Foreign Application Priority Data

Nov. 5, 2010 (KR) ..... 10-2010-0109850

## Publication Classification

(51) Int. Cl.

G09G 3/32 (2006.01)

G09G 3/00 (2006.01)

A pixel may include an organic light emitting diode (OLED) with a cathode electrode coupled to a second power source, a first transistor with a first electrode coupled to a data line, with a second electrode coupled to a first node, the first transistor being turned on when a scan signal is supplied to a scan line, a first capacitor coupled between the first node and a third power source to charge a first capacitor voltage corresponding to a data signal supplied from the data line, and a pixel circuit charged by the first capacitor voltage to supply current corresponding to a charged first power source voltage from a first power source to the second power source via the OLED.

FIG. 1

FIG. 2

FIG. 3A

FIG. 3B

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

## PIXEL AND ORGANIC LIGHT EMITTING DISPLAY USING THE SAME

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This is a divisional application based on pending application Ser. No. 13/137,899, filed Sep. 21, 2011, the entire contents of which is hereby incorporated by reference.

[0002] This application claims priority to and the benefit of Korean Patent Application No. 10-2010-0109850, filed on Nov. 5, 2010, in the Korean Intellectual Property Office, the entire content of which is incorporated herein by reference.

### BACKGROUND

#### [0003] 1. Field

Embodiments relate to a pixel capable of being driven at a low driving frequency and an organic light emitting display using the same.

#### [0005] 2. Description of the Related Art

Recently, various flat panel displays (FPD) capable of reducing weight and volume have been developed. Weight and volume are disadvantages of cathode ray tubes (CRT). The FPDs include liquid crystal displays (LCD), field emission displays (FED), plasma display panels (PDP), and organic light emitting displays.

[0007] The organic light emitting displays display images using organic light emitting diodes (OLED) that generate light by re-combination of electrons and holes. The organic light emitting display has high response speed and is driven with low power consumption.

[0008] The organic light emitting display includes a plurality of data lines, scan lines, and a plurality of pixels arranged in a matrix at intersections of power lines. Each pixel includes an organic light emitting diode, at least two transistors including a drive transistor, and at least one capacitor.

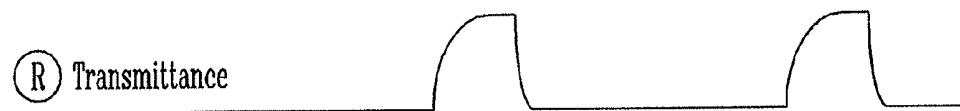

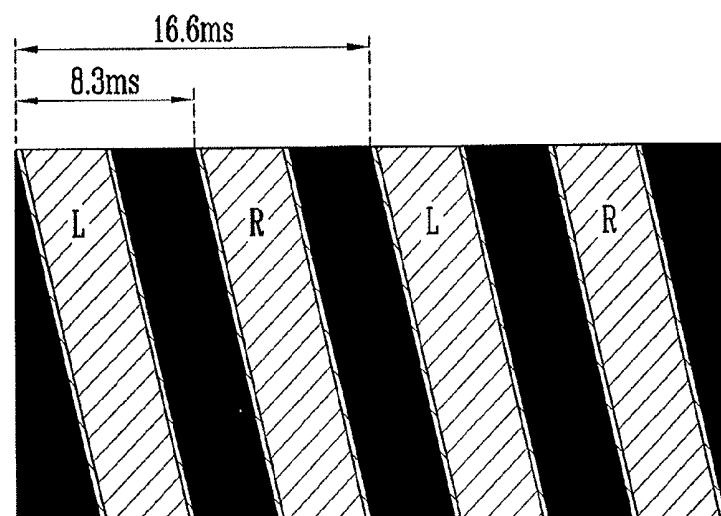

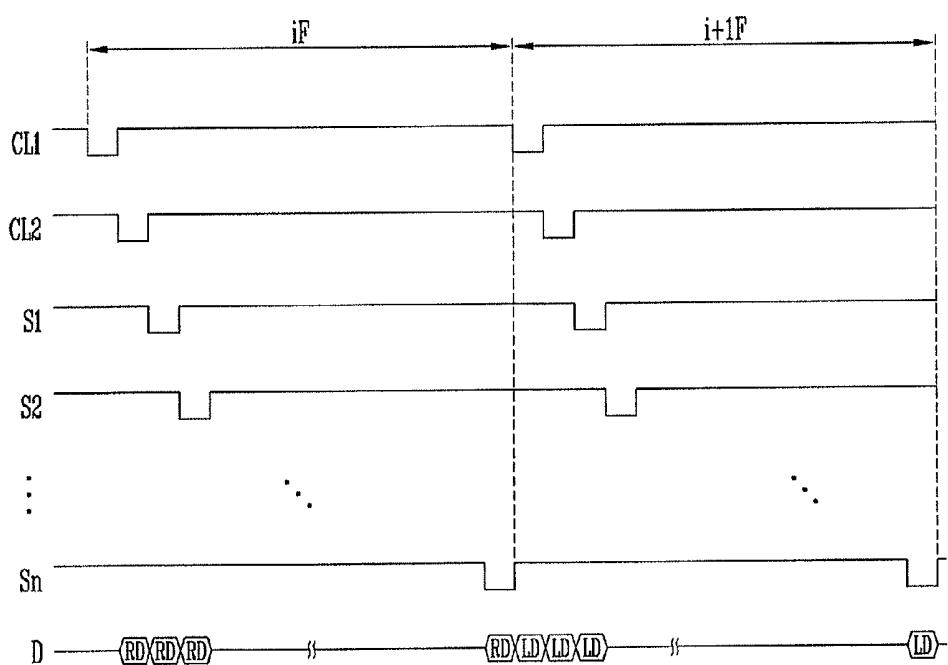

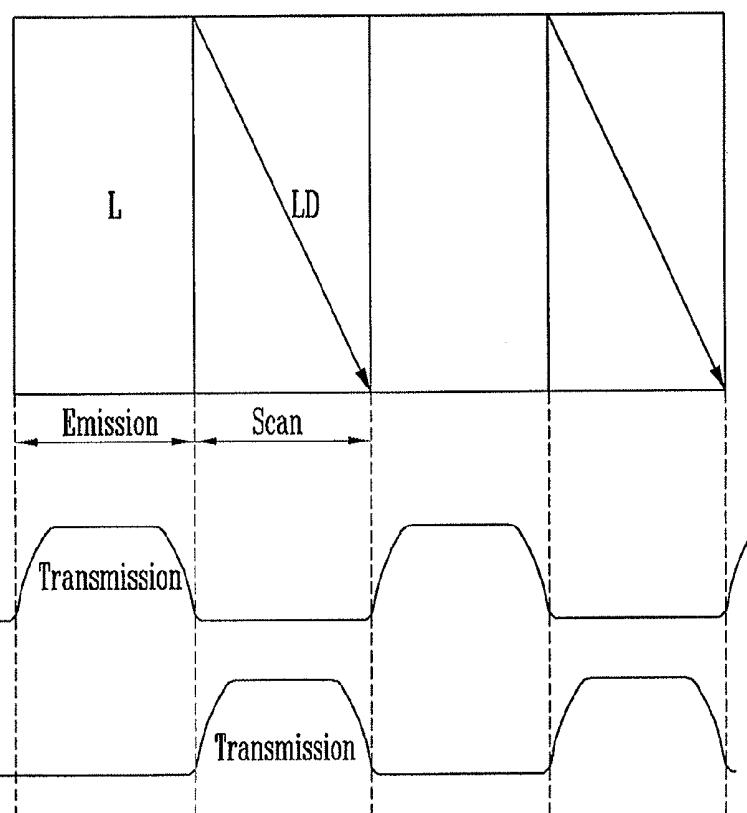

[0009] The organic light emitting display includes four frames in a period of 16.6 ms as illustrated in FIG. 1 in order to realize a 3D image. Among the four frames, a first frame displays a left image and a third frame displays a right image. A second frame and a fourth frame display a black image.

### SUMMARY

[0010] Embodiments are directed to a pixel and an organic light emitting display using the same.

[0011] An embodiment may include a pixel, including an organic light emitting diode (OLED) with a cathode electrode coupled to a second power source, a first transistor with a first electrode coupled to a data line, with a second electrode coupled to a first node, the first transistor being turned on when a scan signal is supplied to a scan line, a first capacitor coupled between the first node and a third power source to charge a first capacitor voltage corresponding to a data signal supplied from the data line, and a pixel circuit charged by the first capacitor voltage, the pixel circuit controls current from a first power source to the second power source via the OLED.

[0012] Another embodiment may include pixels positioned at intersections of scan lines and data lines, a scan driver for sequentially supplying scan signals to the scan lines, a data driver for supplying data signals to the data lines in synchronization with the scan signals, a first control line and a second control line commonly coupled to the pixels, and a control driver for sequentially supplying a first control signal to the first control line and a second control signal to the second

control line in a stage before the scan signals are supplied to the scan lines in frames. Among the pixels, a pixel positioned in a jth horizontal line includes a first capacitor for charging a data signal voltage corresponding to the data signal when, among the scan signals, a scan signal is supplied to a jth scan line and a second capacitor for charging a first capacitor voltage corresponding to the voltage charged in the first capacitor when the second control signal is supplied to the second control line.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0013] The above and other features will become more apparent to those of ordinary skill in the art by describing in detail exemplary embodiments with reference to the attached drawings, in which:

[0014] FIG. 1 illustrates frames for 3D driving;

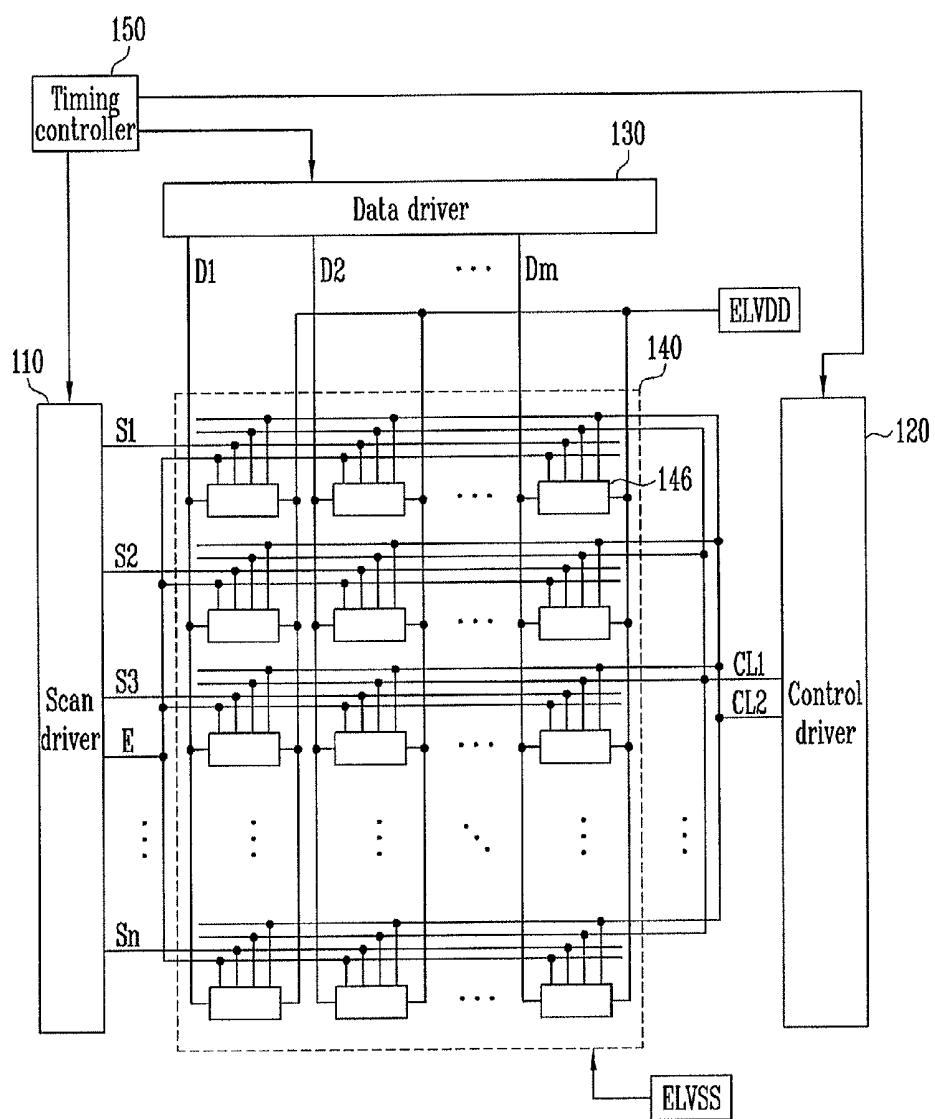

[0015] FIG. 2 illustrates a view of an organic light emitting display according to a first embodiment;

[0016] FIGS. 3A and 3B illustrate views of an embodiment of a pixel of FIG. 2;

[0017] FIG. 4 illustrates a view of an embodiment of the pixel circuit of FIGS. 3A and 3B;

[0018] FIG. 5 illustrates a waveform chart of a method of driving the pixel of FIG. 4;

[0019] FIG. 6 illustrates a view of frames according to present embodiments for 3D driving;

[0020] FIG. 7 illustrates a view of an organic light emitting display according to another embodiment;

[0021] FIG. 8 illustrates a view of an embodiment of the pixel of FIG. 7; and

[0022] FIG. 9 illustrates a waveform chart of a method of driving the pixel of FIG. 8.

### DETAILED DESCRIPTION

[0023] Korean Patent Application No. 10-2010-0109850, filed on Nov. 5, 2010, in the Korean Intellectual Property Office, and entitled: "Pixel and Organic Light Emitting Display Device" is incorporated by reference herein in its entirety.

[0024] Example embodiments will now be described more fully hereinafter with reference to the accompanying drawings; however, they may be embodied in different forms and should not be construed as limited to the embodiments set forth herein.

[0025] Hereinafter, exemplary embodiments, by which those who skilled in the art may easily perform, will be described in detail with reference to FIGS. 2 to 9.

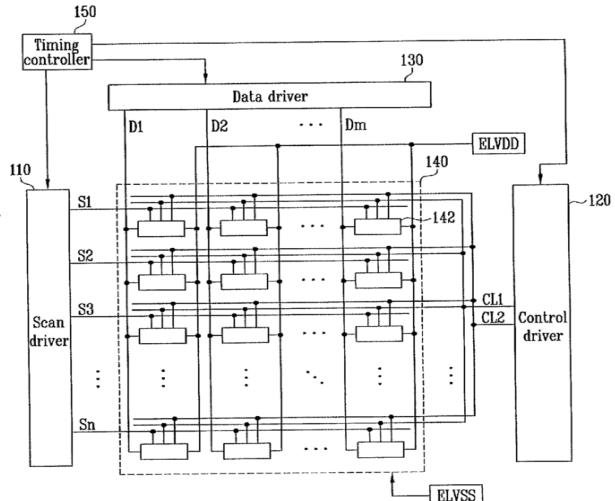

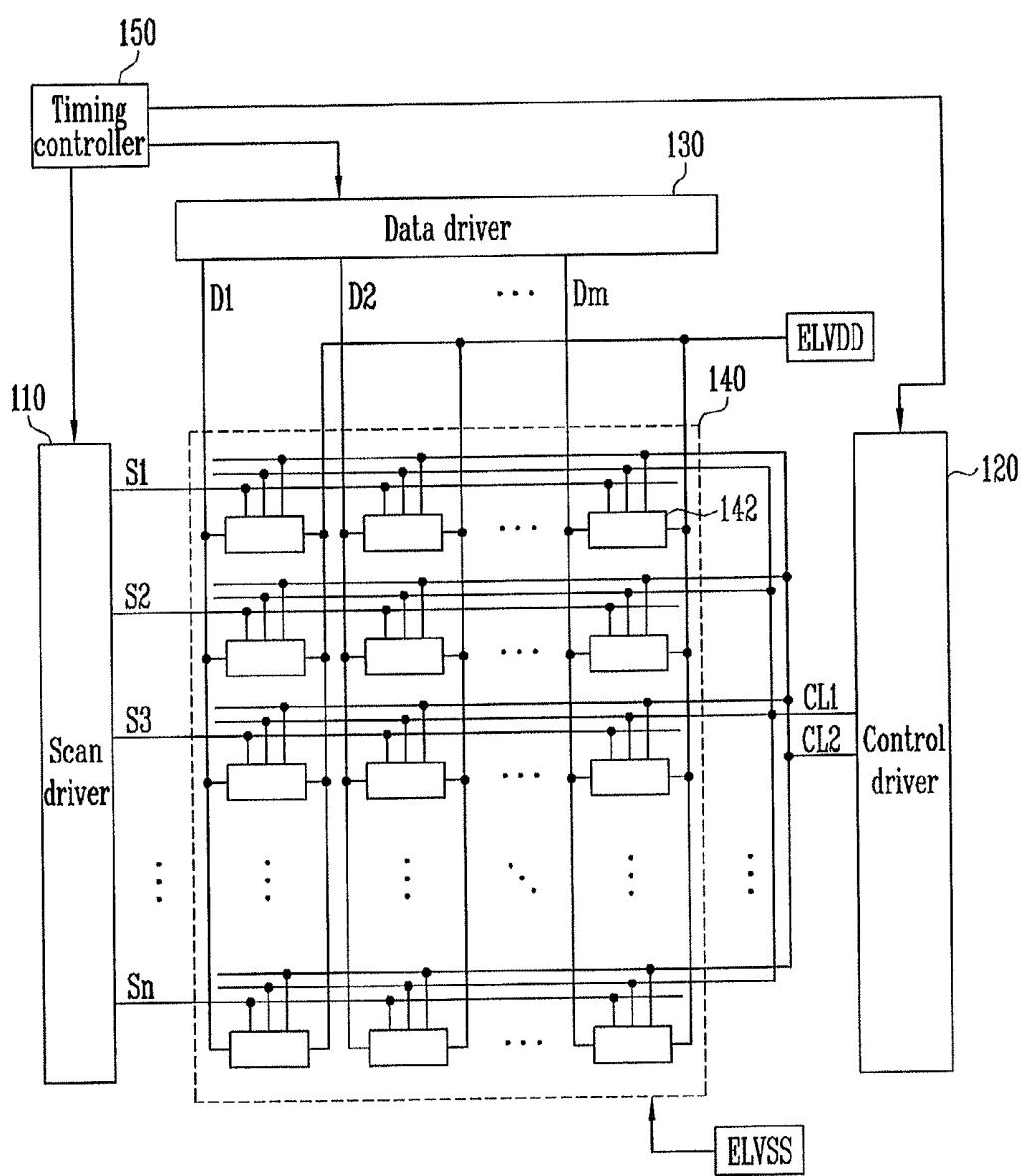

[0026] FIG. 2 is a view illustrating an organic light emitting display according to a first embodiment.

[0027] Referring to FIG. 2, the organic light emitting display according to the first embodiment includes a pixel unit 140 including pixels 142 positioned at the intersections of scan lines S1 to Sn, first control lines CL1, second control lines CL2, and data lines D1 to Dm, a scan driver 110 for driving the scan lines S1 to Sn, a control driver 120 for driving the first control lines CL1 and the second control lines CL2, a data driver 130 for driving the data lines D1 to Dm, and a timing controller 150 for controlling the drivers 110, 120, and 130.

[0028] The scan driver 110 sequentially supplies scan signals to the scan lines S1 to Sn every frame. When the scan signals are supplied to the scan lines S1 to Sn, the pixels 142 are selected in units of horizontal lines.

[0029] The data driver 130 supplies data signals to the data lines D1 to Dm in synchronization with the scan signals. Then, the data signals are supplied to the pixels 142 selected by the scan signals. The data driver 130 alternately supplies left data signals and right data signals every frame. For example, the data driver 130 supplies the right data signals in ith (i is a natural number) frames iF and supplies the left data signals in (i+1)th frames i+1F. The right data signals mean the signals corresponding to the right side of the shutter glasses and the left data signals mean the signals corresponding to the left side of the shutter glasses.

[0030] The control driver 120 supplies a first control signal and a second control signal to the first control lines CL1 and the second control lines CL2 commonly coupled to the pixels 142. The first control signal and the second control signal are supplied at the early stage of each of the frames, i.e., before the scan signals are supplied to the scan lines S1 to Sn.

[0031] The pixels 142 are positioned at the intersections of the scan lines S1 to Sn, the first control lines CL1, the second control lines CL2, and the data lines D1 to Dm. The pixels 142 charge the right data signals to correspond to the scan signals supplied to the scan lines S1 to Sn in the ith frames. The pixels 142 simultaneously emit light components corresponding to the left data signals in the ith frames where the right data signals are charged. In addition, the pixels 142 charge the left data signals to correspond to the scan signals supplied to the scan lines S1 to Sn in the (i+1)th frames. The pixels 142 simultaneously emit light components corresponding to the right data signals in the (i+1)th frames where the left data signals are charged.

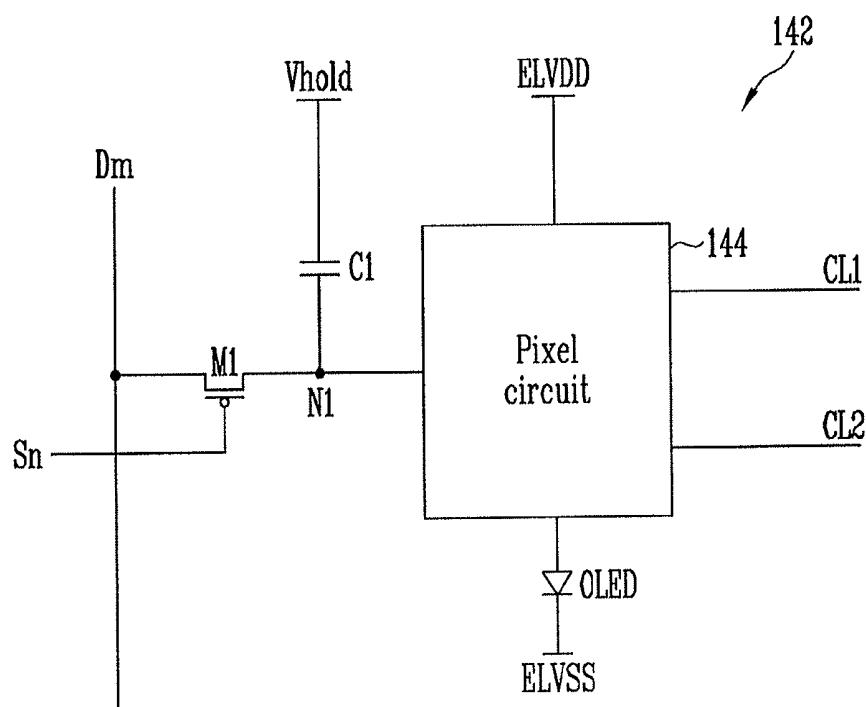

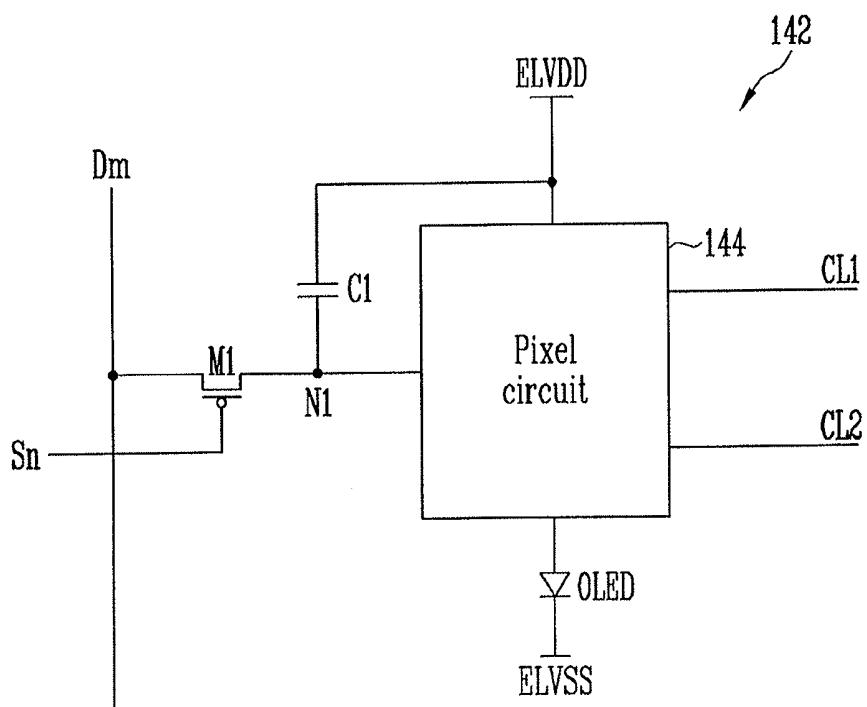

[0032] FIGS. 3A and 3B are views illustrating an embodiment of the pixel of FIG. 2. In FIGS. 3A and 3B, the pixel coupled to the mth data line Dm and the nth scan line Sn will be illustrated.

[0033] Referring to FIG. 3A, the pixel 142 according to the embodiment includes a first transistor M1, a first capacitor C1, a pixel circuit 144, and an organic light emitting diode (OLED).

[0034] The anode electrode of the OLED is coupled to the pixel circuit 144 and the cathode electrode of the OLED is coupled to a second power source ELVSS. The OLED generates light with predetermined brightness to correspond to the amount of current supplied from the pixel circuit 144.

[0035] The first electrode of the first transistor M1 is coupled to the data line Dm and the second electrode of the first transistor M1 is coupled to a first node N1 coupled to the pixel circuit 144. Then, the gate electrode of the first transistor M1 is coupled to the scan line Sn. The first transistor M1 is turned on when a scan signal is supplied to the scan line Sn.

[0036] The first capacitor C1 is coupled between the first node N1 and a third power source Vhold. The first capacitor C1 charges the voltage corresponding to the data signal supplied from the data line Dm when the first transistor M1 is turned on. The third power source Vhold may be set as a fixed power source (i.e., a direct current power source) at a predetermined voltage.

[0037] The third power source Vhold is set to have the same voltage as a first power source ELVDD and may be coupled to the first capacitor C1 through an additional line. In addition, the third power source Vhold may be selected as the first power source ELVDD as illustrated in FIG. 3B and may be selected as one of the various types of power sources (i.e., the initial power source Vint of FIG. 4) supplied to the pixel. For

convenience, it is assumed that the third power source Vhold is selected as the first power source ELVDD.

[0038] The pixel circuit 144 is initialized when the first control signal is supplied to the first control lines CL1 and charges a predetermined voltage to correspond to the voltage charged in the first capacitor C1 when the second control signal is supplied to the second control lines CL2. The pixel circuit 144 that charges a predetermined voltage controls the amount of current supplied to the OLED to correspond to the voltage charged therein. The pixel circuit 144 may be realized by well-known types of various circuits.

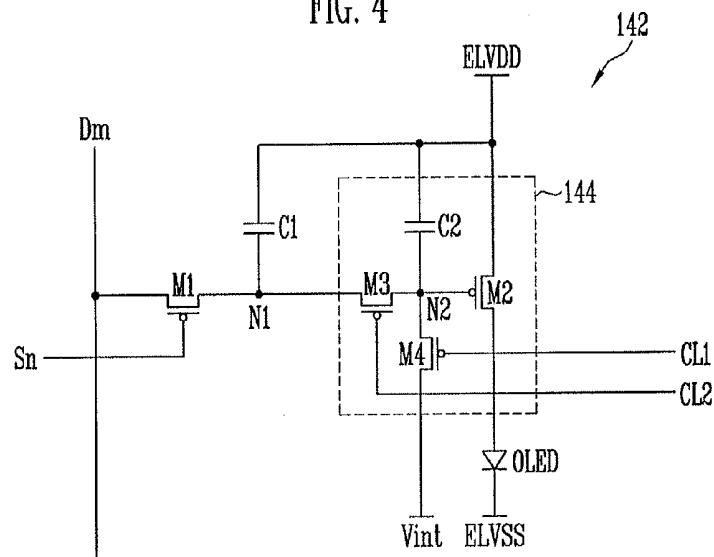

[0039] FIG. 4 is a view illustrating an embodiment of the pixel circuit of FIG. 3.

[0040] Referring to FIG. 4, the pixel circuit 144 includes a second transistor M2, a third transistor M3, a fourth transistor M4, and a second capacitor C2.

[0041] The first electrode of the second transistor M2 is coupled to the first power source ELVDD, the second electrode of the second transistor M2 is coupled to the anode electrode of the OLED, and the gate electrode of the second transistor M2 is coupled to a second node N2. The second transistor M2 supplies the current corresponding to the voltage applied to the second node N2 from the first power source ELVDD to the second power source ELVSS via the OLED.

[0042] The first electrode of the third transistor M3 is coupled to the first node N1 and the second electrode of the third transistor M3 is coupled to the second node N2. Then, the gate electrode of the third transistor M3 is coupled to the second control line CL2. The third transistor M3 is turned on when the second control signal is supplied to the second control line CL2 to electrically couple the first node N1 to the second node N2.

[0043] The first electrode of the fourth transistor M4 is coupled to the second node N2 and the second electrode of the fourth transistor M4 is coupled to the initial power source Vint. Then, the gate electrode of the fourth transistor M4 is coupled to the first control line CL1. The fourth transistor M4 is turned on when the first control signal is supplied to the first control line CL1 to supply the voltage of the initial power source Vint to the second node N2. The initial power source Vint is set to have a lower voltage than the data signal so that the second node N2 is initialized by the voltage of the initial power source Vint when the fourth transistor M4 is turned on.

[0044] The second capacitor C2 is coupled between the second node N2 and the first power source ELVDD. The second capacitor C2 is charged to correspond to the voltage supplied from the first capacitor C1 when the third transistor M3 is turned on.

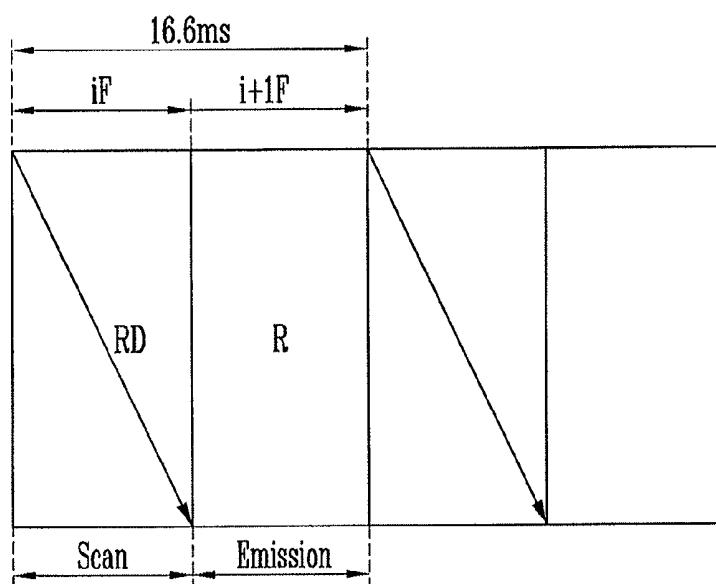

[0045] FIG. 5 is a waveform chart illustrating a method of driving the pixel of FIG. 4. FIG. 6 is a view illustrating frames according to present embodiments for 3D driving.

[0046] Referring to FIGS. 5 and 6, the first control signal is supplied to the first control line CL1 at the early stage of the ith frame iF. When the first control signal is supplied, the fourth transistor M4 is turned on so that the voltage of the initial power source Vint is supplied to the second node N2. When the first control signal is supplied to the first control line CL1, the second node N2 of each of the pixels 142 is set to have the voltage of the initial power source Vint. When the second node N2 of each of the pixels 142 is set to have the voltage of the initial power source Vint before the data signal is supplied, an image with uniform brightness may be displayed.

[0047] After the voltage of the initial power source Vint is supplied to the second node N2, the second control signal is supplied to the second control line CL2 so that the third transistor M3 is turned on. When the third transistor M3 is turned on, the voltage corresponding to the left data signal LD charged in the first capacitor C1 in an (i-1)th frame i-1F is supplied to the second node so that the second capacitor C2 charges the voltage corresponding to the left data signal LD.

[0048] The voltage charged in the second capacitor C2 is determined by the coupling of the first capacitor C1 and the second capacitor C2. Therefore, only the partial voltage charged in the first capacitor C1 is charged in the second capacitor C2 so that an image with desired brightness may not be displayed. Therefore, according to present embodiments, the voltage of the data signal is set considering the coupling of the first capacitor C1 and the second capacitor C2. Then, a higher voltage than a desired voltage is charged in the first capacitor C1 and the desired voltage is charged in the second capacitor C2 that receives the voltage from the first capacitor C1. In addition, according to present embodiments, the first capacitor C1 has a larger capacity than the second capacitor C2 so that the voltage may be stably charged in the second capacitor C2.

[0049] After a predetermined voltage is charged in the second capacitor C2, the second transistor M2 supplies the current corresponding to the voltage charged in the second capacitor C2 to the OLED. At this time, the OLED generates light with predetermined brightness to correspond to the amount of current supplied thereto. The amount of current supplied to the OLED in the ith frame iF is determined to correspond to the left data signal LD supplied in the (i-1)th frame i-1F.

[0050] In the period where the OLED of each of the pixels 142 emits light, scan signals are sequentially supplied to the first scan signal to the nth scan signal Sn. The right data signal RD is supplied to the data lines D1 to Dm in synchronization with the scan signals.

[0051] When a scan signal is supplied to the nth scan line Sn, the first transistor M1 is turned on. When the first transistor M1 is turned on, the right data signal RD from the data line Dm is supplied to the first node N1. At this time, the first capacitor C1 charges the voltage corresponding to the right data signal.

[0052] The OLED emits light to correspond to the left data signal LD supplied to the (i-1)th frame i-1F in the ith frame iF and the first capacitor C1 charges the voltage corresponding to the right data signal RD supplied in the ith frame iF.

[0053] The first control signal is supplied to the first control line CL1 in the (i+1)th frame i+1F so that the second node N2 included in each of the pixels 142 is set to have the voltage of the initial power source Vint. Then, the second control signal is supplied to the second control line CL2 so that the third transistor M3 included in each of the pixels is turned on. When the third transistor M3 is turned on, the second capacitor C2 charges the voltage corresponding to the voltage supplied from the first capacitor C1.

[0054] After a predetermined voltage is charged in the second capacitor C2, the second transistor M2 supplies the current corresponding to the voltage charged in the second capacitor C2 to the OLED. At this time, the OLED generates light with predetermined brightness to correspond to the amount of current supplied thereto. The amount of current

supplied to the OLED in the (i+1)th frame i+1F is determined to correspond to the right data signal RD supplied in the ith frame iF.

[0055] While the scan signals are sequentially supplied to the first scan line S1 to the nth scan line Sn, the first transistor M1 included in each of the pixels 142 is turned on in units of horizontal lines. At this time, the left data signals LD are supplied to the data lines D1 to Dm in synchronization with the scan signals. Therefore, the voltage corresponding to the left data signal LD is charged in the first capacitor C1 included in each of the pixels 142 in the (i+1)th frame i+1F.

[0056] As described above, according to present embodiments, the pixels 142 alternately generate light components corresponding to the left and right data signals in the frames. While the pixels 142 generate light components corresponding to the left (or right) data signals, the voltages corresponding to the right (or left) data signals are charged. While the pixels 142 according to present embodiments emit light, the voltages corresponding to the data signals are charged so that the left images and the right images may be alternately generated every frame. In this case, according to present embodiments, as illustrated in FIG. 6, a 3D image may be realized at the driving frequency of 120 Hz.

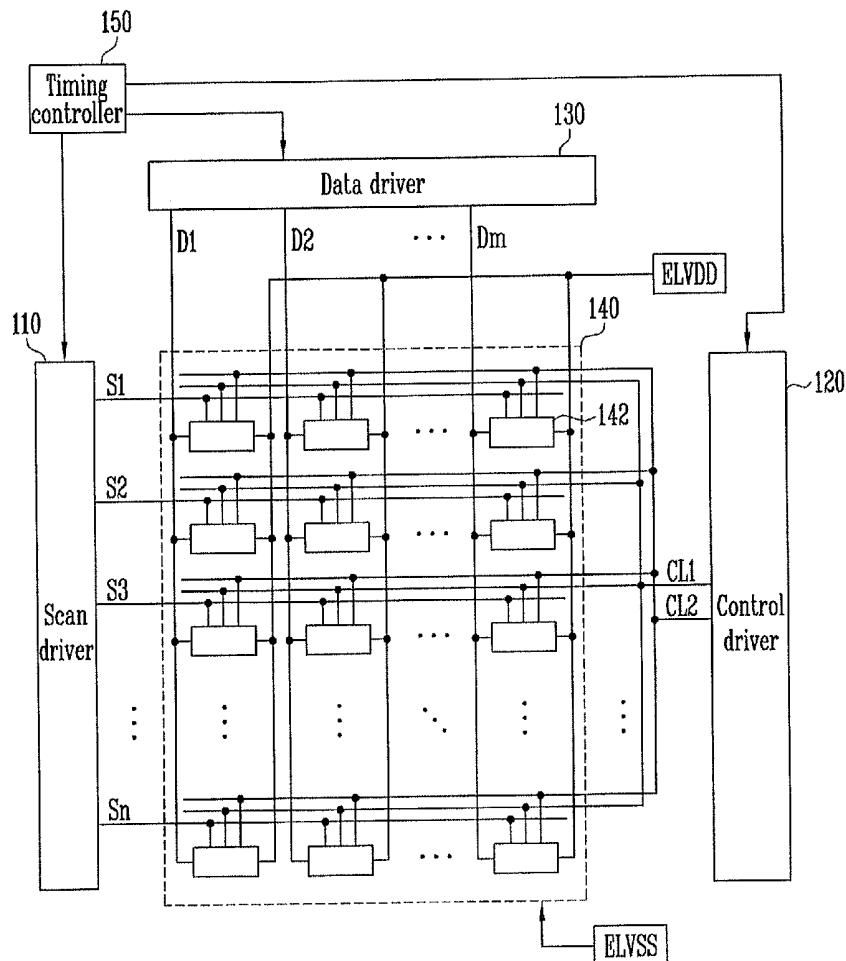

[0057] FIG. 7 is a view illustrating an organic light emitting display according to a second embodiment. When FIG. 7 is described, the same elements as those of FIG. 2 are denoted by the same reference numerals and detailed description thereof will be omitted.

[0058] Referring to FIG. 7, the organic light emitting display according to the second embodiment further includes an emission control line E to be commonly coupled to the pixels 146. The emission control line E receives the emission control signal from the scan driver 110 to transmit the emission control signal to the pixels 146.

[0059] In the organic light emitting display according to the second embodiment, the emission control line E is added to the circuit structure of the pixels 146 and the other structures are the same those of FIG. 2.

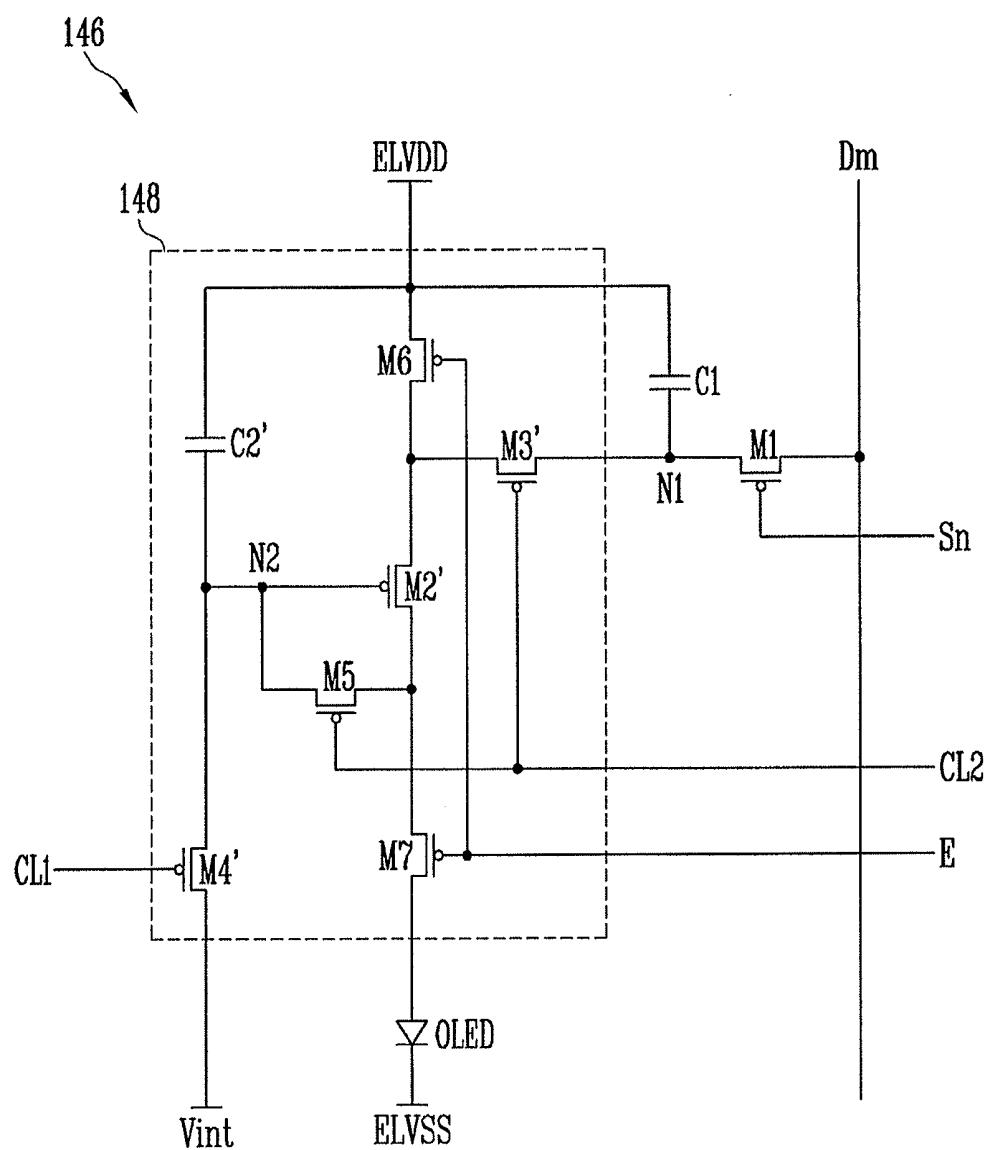

[0060] FIG. 8 is a view illustrating an embodiment of the pixel of FIG. 7. When FIG. 8 is described, the same elements as those of FIG. 4 are denoted by the same reference numerals and detailed description thereof will be omitted.

[0061] Referring to FIG. 8, a pixel circuit 148 includes second to seventh transistors M2' to M7 and a second capacitor C2'.

[0062] The first electrode of the second transistor M2' is coupled to the second electrode of the sixth transistor M6 and the second electrode of the second transistor M2' is coupled to the first electrode of the seventh transistor M7. Then, the gate electrode of the second transistor M2' is coupled to the second node N2. The second transistor M2' supplies the current corresponding to the voltage applied to the second node N2 from the first power source ELVDD to the second power source ELVSS via the OLED.

[0063] The first electrode of the third transistor M3' is coupled to the first node N1 and the second electrode of the third transistor M3' is coupled to the first electrode of the second transistor M2'. The gate electrode of the third transistor M3' is coupled to the second control line CL2. The third transistor M3' is turned on when the second control signal is supplied to the second control line CL2 to electrically couple the first node N1 to the first electrode of the second transistor M2'.

[0064] The first electrode of the fourth transistor M<sub>4'</sub> is coupled to the second node N<sub>2</sub> and the second electrode of the fourth transistor M<sub>4'</sub> is coupled to the initial power source Vint. Then, the gate electrode of the fourth transistor M<sub>4'</sub> is coupled to the first control line CL<sub>1</sub>. The fourth transistor M<sub>4'</sub> is turned on when the first control signal is supplied to the first control line CL<sub>1</sub> to supply the voltage of the initial power source Vint to the second node N<sub>2</sub>.

[0065] The first electrode of the fifth transistor M<sub>5</sub> is coupled to the second electrode of the second transistor M<sub>2'</sub> and the first electrode of the fifth transistor M<sub>5</sub> is coupled to the second node N<sub>2</sub>. The gate electrode of the fifth transistor M<sub>5</sub> is coupled to the second control line CL<sub>2</sub>. The fifth transistor M<sub>5</sub> is turned on when the second control signal is supplied to the second control line CL<sub>2</sub> to couple the second transistor M<sub>2'</sub> in the form of a diode.

[0066] The first electrode of the sixth transistor M<sub>6</sub> is coupled to the first power source ELVDD and the second electrode of the sixth transistor M<sub>6</sub> is coupled to the first electrode of the second transistor M<sub>2'</sub>. The gate electrode of the sixth transistor M<sub>6</sub> is coupled to the emission control line E. The sixth transistor M<sub>6</sub> is turned off when the emission control signal is supplied to the emission control line E and is turned on when the emission control signal is not supplied.

[0067] The first electrode of the seventh transistor M<sub>7</sub> is coupled to the second electrode of the second transistor M<sub>2'</sub> and the second electrode of the seventh transistor M<sub>7</sub> is coupled to the anode electrode of the OLED. The gate electrode of the seventh transistor M<sub>7</sub> is coupled to the emission control line E. The seventh transistor M<sub>7</sub> is turned off when the emission control signal is supplied to the emission control line E and is turned on when the emission control signal is not supplied to the emission control line E.

[0068] The second capacitor C<sub>2'</sub> is coupled between the second node N<sub>2</sub> and the first power source ELVDD. The second capacitor C<sub>2'</sub> is charged to correspond to the voltage supplied from the first capacitor C<sub>1</sub> when the third transistor M<sub>3'</sub> and the fifth transistor M<sub>5'</sub> are turned on.

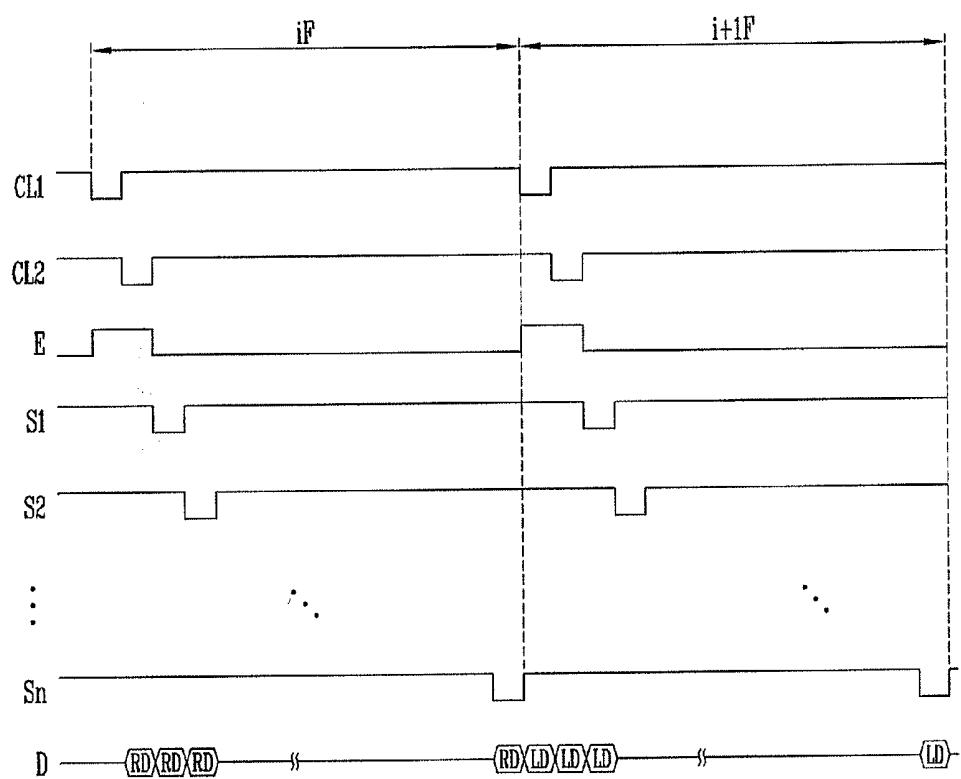

[0069] FIG. 9 is a waveform chart illustrating a method of driving the pixel of FIG. 8.

[0070] Referring to FIG. 9, the first control signal and the second control signal are sequentially supplied to the first control line CL<sub>1</sub> and the second control line CL<sub>2</sub> at the early stage of the i<sup>th</sup> frame iF. Then, the emission control signal is supplied to the emission control line E to overlap the first control signal and the second control signal.

[0071] When the emission control signal is supplied to the emission control line E, the sixth transistor M<sub>6</sub> and the seventh transistor M<sub>7</sub> are turned off. When the sixth transistor M<sub>6</sub> is turned off, the first power source ELVDD and the second transistor M<sub>2'</sub> are electrically blocked. When the seventh transistor M<sub>7</sub> is turned off, the second power source ELVSS and the second transistor M<sub>2'</sub> are electrically blocked.

[0072] When the first control signal is supplied to the first control line CL<sub>1</sub>, the fourth transistor M<sub>4'</sub> is turned on. When the fourth transistor M<sub>4'</sub> is turned on, the voltage of the initial power source Vint is supplied to the second node N<sub>2</sub>.

[0073] After the voltage of the initial power source Vint is supplied to the second node N<sub>2</sub>, the second control signal is supplied to the second control line CL<sub>2</sub> so that the third transistor M<sub>3'</sub> and the fifth transistor M<sub>5</sub> are turned on. When the third transistor M<sub>3'</sub> is turned on, the voltage correspond-

ing to the left data signal LD charged in the first capacitor C<sub>1</sub> in the (i-1)<sup>th</sup> frame i-1F is supplied to the first electrode of the second transistor M<sub>2'</sub>.

[0074] At this time, since the second node N<sub>2</sub> is initialized to the voltage of the initial power source Vint lower than the data signals, the second transistor M<sub>2'</sub> coupled in the form of a diode is turned on. When the second transistor M<sub>2'</sub> is turned on, the voltage obtained by subtracting the threshold voltage of the second transistor M<sub>2'</sub> from the voltage applied to the first electrode of the second transistor M<sub>2'</sub> is supplied to the second node N<sub>2</sub>. At this time, the second capacitor C<sub>2'</sub> charges the voltage corresponding to the voltage applied to the second node N<sub>2</sub>. The second capacitor C<sub>2'</sub> charges the voltages corresponding to the left data signal LD supplied in the (i-1)<sup>th</sup> frame i-1F and the threshold voltage of the second transistor M<sub>2'</sub>.

[0075] After the voltages are charged in the second capacitor C<sub>2'</sub>, the supply of the emission control signal to the emission control line E is stopped. For example, the supply of the emission control signal to the emission control line E is stopped before a scan signal is supplied to the first scan line S<sub>1</sub>. When the supply of the emission control signal to the emission control line E is stopped, the sixth transistor M<sub>6</sub> and the seventh transistor M<sub>7</sub> are turned on.

[0076] When the sixth transistor M<sub>6</sub> is turned on, the first power source ELVDD and the first electrode of the second transistor M<sub>2'</sub> are electrically coupled to each other. When the seventh transistor M<sub>7</sub> is turned on, the second electrode of the second transistor M<sub>2'</sub> and the anode electrode of the OLED are electrically coupled to each other. At this time, the second transistor M<sub>2'</sub> controls the amount of current that flows from the first power source ELVDD to the second power source ELVSS via the OLED to correspond to the voltage applied to the second node N<sub>2</sub>. That is, in the i<sup>th</sup> frame iF, the pixels 142 emit light to correspond to the left data signal LD supplied in the (i-1)<sup>th</sup> frame i-1F.

[0077] The scan signals are sequentially supplied to the first scan line S<sub>1</sub> to the nth scan line S<sub>n</sub>. Then, the right data signals RD are supplied to the data lines D<sub>1</sub> to D<sub>m</sub> in synchronization with the scan signals. When the scan signals are sequentially supplied to the scan lines S<sub>1</sub> to S<sub>n</sub>, the first transistors M<sub>1</sub> included in the pixels 146 in units of horizontal lines are turned on. At this time, the right data signals RD from the data lines D<sub>1</sub> to D<sub>m</sub> are supplied to the first nodes N<sub>1</sub> via the first transistors M<sub>1</sub>. Then, the voltages corresponding to the right data signals RD are charged in the first capacitors C<sub>1</sub> included in the pixels 146.

[0078] In the (i+1)<sup>th</sup> frame i+1F, the first control signal and the second control signal are sequentially supplied to the first control line CL<sub>1</sub> and the second control line CL<sub>2</sub>. Then, the emission control signal is supplied to the emission control line E to overlap the first control signal and the second control signal.

[0079] When the emission control signal is supplied to the emission control line E, the sixth transistor M<sub>6</sub> and the seventh transistor M<sub>7</sub> are turned off. When the first control signal is supplied to the first control line CL<sub>1</sub>, the fourth transistor M<sub>4'</sub> is turned on so that the voltage of the initial power source Vint is supplied to the second node N<sub>2</sub>.

[0080] After the voltage of the initial power source Vint is supplied to the second node N<sub>2</sub>, the second control signal is supplied to the second control line CL<sub>2</sub> so that the third transistor M<sub>3'</sub> and the fifth transistor M<sub>5</sub> are turned on. When the third transistor M<sub>3'</sub> and the fifth transistor M<sub>5</sub> are turned

on, the voltage obtained by subtracting the threshold voltage of the second transistor M2' from the voltage applied to the first electrode of the second transistor M2' is supplied to the second node N2. At this time, the second capacitor C2' charges the voltages corresponding to the right data signal RD supplied in the ith frame iF and the threshold voltage of the second transistor M2'.

[0081] After the voltages of the second capacitor C2' are charged, the supply of the emission control signal to the emission control line E is stopped so that the sixth transistor M6 and the seventh transistor M7 are turned on. When the sixth transistor M6 is turned on, the first power source ELVDD and the first electrode of the second transistor M2' are electrically coupled to each other. When the seventh transistor M7 is turned on, the second electrode of the second transistor M2' and the anode electrode of the OLED are electrically coupled to each other. At this time, the second transistor M2 controls the amount of current that flows from the first power source ELVDD to the second power source ELVSS via the OLED to correspond to the voltage applied to the second node N2. In the (i+1)th frame i+1F, the pixels 142 emit light to correspond to the right data signals RD supplied in the ith frame iF.

[0082] The scan signals are sequentially supplied to the first scan line S1 to the nth scan line Sn. The left data signals LD are supplied to the data lines D1 to Dm in synchronization with the scan signals. When the scan signals are sequentially supplied to the scan lines S1 to Sn, the first transistors M1 included in the pixels 146 in units of horizontal lines are turned on. At this time, the left data signals LD from the data lines D1 to Dm are supplied to the first nodes N1 through the first transistors M1. Then, the first capacitor C1 included in the pixels 146 charge the voltages corresponding to the left data signals LD.

[0083] By way of summation and review, shutter glasses receive light from a left glass in the first frame among four frames and receive light from a right glass in the third frame. At this time, the person who wears the shutter glasses recognizes the 3D image supplied through the shutter glasses. The black image displayed in the second frame and the fourth frame prevents a left image and a right image from being mixed with each other. If the left image and the right image are mixed, crosstalk may be generated.

[0084] In order to have the four frames included in the period of 16.6 ms, the organic light emitting display must be driven at the driving frequency of 240 Hz. When the organic light emitting display is driven at a high frequency, power consumption increases, stability deteriorates, and manufacturing cost increases.

[0085] Circumventing such situations, present embodiments are directed to a pixel capable of being driven at a low driving frequency, and an organic light emitting display using the same.

[0086] In the pixel according to present embodiments and the organic light emitting display using the same, the pixels emit light and the data signals may be simultaneously charged so that the organic light emitting display may realize the 3D image while being driven at the low driving frequency.

[0087] Example embodiments have been disclosed herein, and although specific terms are employed, they are used and are to be interpreted in a generic and descriptive sense only and not for purpose of limitation.

**1.-23. (canceled)**

**24. A pixel, comprising:**

an organic light emitting diode (OLED) including a first electrode coupled to a second power source; a first transistor coupled between a data line and a first node; a second transistor including a first electrode, a second electrode and a gate electrode; a third transistor coupled between the first node and the first electrode of the second transistor; a fourth transistor coupled between the gate electrode of the second transistor and an initial power source; a fifth transistor coupled between the second electrode of the second transistor and the gate electrode of the second transistor; a sixth transistor coupled between the first electrode of the second transistor and a first power source; a seventh transistor coupled between the second electrode of the second transistor and the OLED; a first capacitor coupled between the first node and a third power source; and a second capacitor coupled between the gate electrode of the second transistor and the first power source.

**25. The pixel as claimed in claim 24, wherein the first transistor is turned on when a scan signal is supplied to a scan line.**

**26. The pixel as claimed in claim 25, wherein the third transistor is turned on before the first transistor is turned on in a frame.**

**27. The pixel as claimed in claim 26, wherein the fifth transistor is simultaneously turned on and off with the third transistor.**

**28. The pixel as claimed in claim 26, wherein the fourth transistor is turned on before the third transistor is turned on in the frame.**

**29. The pixel as claimed in claim 28, wherein the sixth transistor is turned off when the third transistor and the fourth transistor are turned on in the frame.**

**30. The pixel as claimed in claim 29, wherein the seventh transistor is simultaneously turned on and off with the sixth transistor.**

**31. The pixel as claimed in claim 24, wherein the third power source is the first power source or the initial power source.**

**32. An organic light emitting display, comprising:**

a scan line; a data line; a first control line; a second control line; an emission control line; and a pixel coupled to the scan line, the data line, the first control line, the second control line, and the emission control line,

wherein the pixel includes:

an organic light emitting diode (OLED) including a first electrode coupled to a second power source; a first transistor coupled between the data line and a first node; a second transistor including a first electrode, a second electrode and a gate electrode; a third transistor coupled between the first node and the first electrode of the second transistor; a fourth transistor coupled between the gate electrode of the second transistor and an initial power source;

- a fifth transistor coupled between the second electrode of the second transistor and the gate electrode of the second transistor;

- a sixth transistor coupled between the first electrode of the second transistor and a first power source;

- a seventh transistor coupled between the second electrode of the second transistor and the OLED;

- a first capacitor coupled between the first node and a third power source; and

- a second capacitor coupled between the gate electrode of the second transistor and the first power source.

- 33.** The organic light emitting display as claimed in claim 32,

- wherein the scan line is coupled to a gate electrode of the first transistor, and

- wherein the first transistor is turned on when a scan signal is supplied to the scan line.

- 34.** The organic light emitting display as claimed in claim 33,

- wherein the first control line is coupled to a gate electrode of the fourth transistor, and

- wherein the fourth transistor is turned on when a first control signal is supplied to the first control line.

- 35.** The organic light emitting display as claimed in claim 34,

- wherein the second control line is coupled to a gate electrode of the third transistor and a gate electrode of the fifth transistor, and

- wherein the third transistor and the fifth transistor are turned on when a second control signal is supplied to the second control line.

- 36.** The organic light emitting display as claimed in claim 35,

- wherein the emission control line is coupled to a gate electrode of the sixth transistor and a gate electrode of the seventh transistor, and

- wherein the sixth transistor and the seventh transistor are turned off when an emission control signal is supplied to the emission control line.

- 37.** The organic light emitting display as claimed in claim 36, wherein the first control signal is supplied to the first control line before the second control signal is supplied to the second control line in a frame.

- 38.** The organic light emitting display as claimed in claim 37, wherein the emission control signal overlaps the first control signal and the second control signal.

- 39.** The organic light emitting display as claimed in claim 32, wherein the third power source is the first power source or the initial power source.

- 40.** A pixel, comprising:

- an organic light emitting diode (OLED) with a first electrode coupled to a second power source;

- a first transistor with a first electrode coupled to a data line, and with a second electrode coupled to a first node, the first transistor being turned on when a scan signal is supplied to a scan line;

- a first capacitor coupled between the first node and a third power source, the first capacitor to charge a first capacitor voltage corresponding to a data signal supplied from the data line;

- a second capacitor coupled between a second node and a first power source, the second capacitor to charge a second capacitor voltage according to the first capacitor voltage charged in the first capacitor;

- a second transistor to drive the OLED to flow current corresponding to the second capacitor voltage charged in the second capacitor through the OLED, the second transistor coupled between the first power source and a second electrode of the OLED and having a gate electrode connected to the second node;

- a third transistor coupled between the first node and a first electrode of the second transistor;

- a fourth transistor coupled between the gate electrode of the second transistor and an initial power source and turned on before the third transistor is turned on; and

- a fifth transistor coupled between a second electrode of the second transistor and the gate electrode of the second transistor and simultaneously turned on and off with the third transistor;

- wherein when the first capacitor voltage corresponding to the data signal is charged in the first capacitor, the first transistor is turned on and the third transistor is turned off.

- 41.** The pixel as claimed in claim 40, wherein the third transistor is turned on before the first transistor is turned on in a frame.

- 42.** The pixel as claimed in claim 40, further comprising:

- a sixth transistor coupled between the first electrode of the second transistor and the first power source and turned off when the third transistor and the fourth transistor are turned on in the frame and turned on in other periods; and

- a seventh transistor coupled between the second electrode of the second transistor and the OLED and simultaneously turned on and off with the sixth transistor.

\* \* \* \* \*

|                |                                                                                                                                            |                       |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|

| 专利名称(译)        | 使用其的像素和有机发光显示器                                                                                                                             |                       |            |

| 公开(公告)号        | <a href="#">US20160171927A1</a>                                                                                                            | 公开(公告)日               | 2016-06-16 |

| 申请号            | US15/051715                                                                                                                                | 申请日                   | 2016-02-24 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                   |                       |            |

| 申请(专利权)人(译)    | 三星DISPLAY CO. , LTD.                                                                                                                       |                       |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO. , LTD.                                                                                                                       |                       |            |

| [标]发明人         | KANG CHUL KYU                                                                                                                              |                       |            |

| 发明人            | KANG, CHUL-KYU                                                                                                                             |                       |            |

| IPC分类号         | G09G3/32 G09G3/00                                                                                                                          |                       |            |

| CPC分类号         | G09G3/325 G09G3/3266 G09G3/003 G09G2330/00 G09G2300/0439 G09G2300/0809 G09G2310/08<br>G09G2300/0426 G09G3/3233 G09G2300/0852 G09G2300/0861 |                       |            |

| 优先权            | 1020100109850 2010-11-05 KR                                                                                                                |                       |            |

| 其他公开文献         | US9747838                                                                                                                                  |                       |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                  | <a href="#">USPTO</a> |            |

**摘要(译)**

像素可包括：有机发光二极管（OLED），其阴极电极耦合到第二电源；第一晶体管，其中第一电极耦合到数据线，第二电极耦合到第一节点，第一晶体管是当扫描信号被提供给扫描线时，第一电容器连接在第一节点和第三电源之间，以对应于从数据线提供的数据信号对应的第一电容器电压，以及由第一电容器电压通过OLED提供对应于从第一电源到第二电源的充电的第一电源电压的电流。